台积电3DFabric技术助力楷登电子实现高性能先进封装IP流片

【本站】6月9日消息,楷登电子(Cadence)日前宣布在台积电3纳米(N3E)工艺技术基础上成功流片其最新的Cadence 16G UCIe 2.5D先进封装IP。这款IP采用了台积电的3DFabric CoWoS-S硅中介层技术,能够提供超高的带宽密度、高效的低功耗性能以及卓越的低延迟,非常适合需要极高算力的应用场景。

Cadence的UCIe IP为裸片到裸片通信提供了开放标准,随着人工智能/机器学习(AI/ML)、移动、汽车、存储和网络应用推动从单片集成向系统级封装(SiP)Chiplet的转变,裸片到裸片通信变得越来越重要。目前,Cadence正在与许多客户合作,其中包括使用N3E工艺的UCIe先进封装IP的测试芯片已经开始发货并可供使用。这个预先验证的解决方案可以实现快速集成,为客户节省时间和精力。

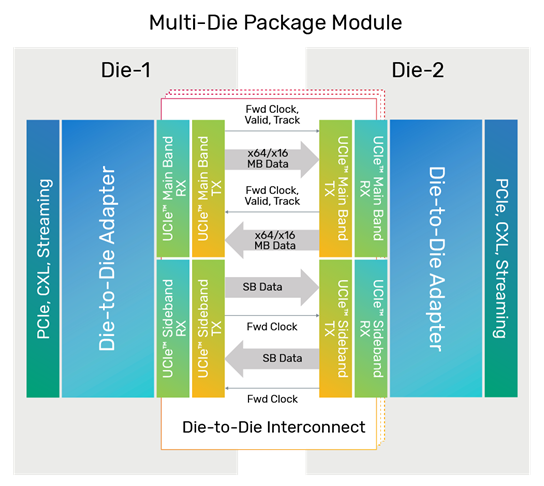

Cadence的UCIe PHY和控制器的异构集成简化了Chiplet解决方案,并具有裸片可重复使用性。完整的解决方案包括UCIe先进封装PHY、UCIe标准封装PHY和UCIe控制器等。UCIe先进封装PHY专为支持5Tbps/mm以上Die边缘带宽密度而设计,能够在显著提高能效的同时实现更高的吞吐量性能,并可以灵活集成到多种类型的2.5D先进封装中。UCIe标准封装PHY则可以帮助客户降低成本,同时保持高带宽和高能效。而UCIe控制器则是一种软IP核,可以在多个技术节点进行综合,并支持多种选项,如流、PCI Express(PCIe)和CXL协议。

据本站了解,UCIe联盟主席Debendra Das Sharma博士表示:“UCIe联盟支持各公司设计用于标准和先进封装的Chiplet。我们非常高兴地祝贺Cadence在实现先进封装测试芯片的流片里程碑上取得的成就,该芯片使用基于UCIe 1.0规范的die-to-die互连。成员公司在IP(扩展)和VIP(测试)方面的进展是该生态系统中的重要组成部分。再加上UCIe工作组的成果,业界将继续看到基于开放行业标准的新Chiplet设计进入市场,促进互操作性、兼容性和创新。”

Cadence一直是Chiplet系统解决方案产品领域的先驱,并将继续推动先进节点和封装架构中各种多Chiplet应用的性能和能效极限。Cadence的全球副总裁兼IP事业部总经理Sanjive Agarwala表示:“我们认为,协调整个行业的互连标准十分重要,而UCIe IP可作为桥梁,为大型系统级芯片提供开放式Chiplet解决方案,达到或超过制造的最大光罩极限。基于台积电N3E工艺的UCIe先进封装流片是为客户提供开放式Chiplet连接标准的关键里程碑和承诺。”

Cadence 16G UCIe 2.5D先进封装IP支持Cadence的智能系统设计(Intelligent System Design™)战略,该战略旨在实现SoC的卓越设计。

相关文章

- 立讯预计最快在 2023 年第一季度开始出货苹果 iPhone14 Pro

- 贵南高铁贵州段联调联试成功结束,进入运行试验阶段

- 贵南高铁接触网全线贯通,为下一步线路送电和联调联试打下基础

- 银兰高铁今日全线开通运营:银川至兰州最快 2 小时 56 分可达

- 集大原高铁山西段建设取得新进展:设计时速 250 公里

- 冲击400公里时速!成渝中线高铁马上开工 投资733亿元

- 跨越时代的发展历程:比亚迪新能源汽车的辉煌征程

- 四年后再次上演:腾讯再次提起多闪用户数据归属诉讼

- 本土品牌崛起 日本汽车巨头在中国市场遭受挑战

- X社交媒体平台推出多项敏感度调整选项,广告商定制品牌安全策略

- 《逆水寒》与《巅峰极速》表现亮眼 网易移动游戏再度崛起

- 智能体验升级 华为HarmonyOS 4引领操作系统创新!

- 火星洞察号数据揭示:火星自转加速现象!

- 6月全球半导体销售额增长1.7% 逆势上扬

- 快速探索数据 亚马逊云科技将大语言模型与QuickSight Q相结合

- 好莱坞罢工预计几周内结束,华纳兄弟探索公司节省数亿美元